# 高速メモリ回路基板の設計・評価に関する研究

本多春樹\* 戸枝 保\* 萩原 玄\*\* 猪瀬 譲\*\*

# A Study on Developing and Designing Printed Circuit Board of High-speed Memory

HONDA Haruki\*, TOEDA Tamotsu\*, HAGIWARA Gen\*\*, INOSE Yuzuru\*\*

#### 抄録

高速メモリに対応したプリント基板を開発するには、厳しいタイミングの制約をクリア することが必須である。配線間の遅延時間の変動の要因は様々であるが、本研究ではミア ンダ、クロストーク及びスルーホールを対象とした。

クロストークにおいては、遅延時間の変動幅が、2線の長さに比例し、2線間の距離に反 比例する結果を得た。

ミアンダにおいては、一定の規模のミアンダにおいて、遅延時間の計算値からの短縮は コーナーの回数を抑え、配線間の距離を広くしたほうが減少する結果を得た。

スルーホールにおいては、単純な配線長さにより見積もられる遅延時間よりも遅延が増加する結果を得た。

キーワード: DDR、タイミングバジェット、タイミング制約、クロストーク、ミアンダ、 スルーホール、遅延時間、タイムドメイン、逆フーリエ変換、信号品質

## 1 はじめに

DDRメモリは汎用PCの市場では普及が進んでいるが、各用途にカスタマイズされた組込機器向けにも用いられる機会が増えつつある。動作基板のリファレンスデザインはJEDEC<sup>1)</sup>から公開されているものの、PC用のモジュールのものであるため、組込機器においては個別に設計をしなくてはならない。しかしながら、高速動作を実現するためには、高周波特性を意識した設計が必要であり、従来の基板設計以上に専門知識・ノウハウが求められている。

DDR2において、クロックーデータ間のタイミングを制約する要因には送信・受信デバイス側

セットアップ・ホールド時間と基板側のスキューなどが挙げられる。更に、基板側のスキューに関していえば、以下の要因が挙げられる<sup>2)</sup>。

- ・ISI (シンボル間干渉)

- ・クロストーク

- 配線長不整合

DRAM製造メーカーの設計例によれば、266 MHzクロックにおいて、データ信号 (DQ) 間のクロストークの時間変動許容値 (以下、タイミングバジェットとよぶ) は、理想的なDQSに対して $\pm 55$  ps、配線長不整合においては $\pm 25$  psと非常に厳しい<sup>2)</sup>。

本研究ではクロストークと配線長不整合(ミアンダ、スルーホール)に関して、実験基板を作成し、遅延時間の変動と上記のタイミングバジェットとの比較を行った。

<sup>\*</sup> 試験研究室 電子技術·電磁波測定担当

<sup>\*\*</sup> リンクサーキット (株)

① 2 つの線路に同方向の信号を入力したときのクロストークについて評価を行った。被誘導ラインの立ち上がり時間は誘導ラインの信号の状態により変動することが知られている <sup>3)</sup>。立ち上がり時間の変動により、遅延時間についても変動が生じる。このときの遅延時間の最大値と最小値の差(以下、遅延時間の変動幅)について検証を行った。

- ② 配線長不整合に対しては、ミアンダにより 配線長の補正を行うことが用いられているが、幾 何学的な配線長と電気的な長さは異なる。そのた め幾何学的な等長配線をおこなっても、意図した とおりに遅延を補正することが出来ない。そこで、 本研究ではミアンダによる遅延時間の変化につい て検証を行った。

- ③ また、DDR2において多層基板が用いられるため、スルーホールが遅延時間に与える影響についても検証を行った。

## 2 実験方法

前章の①~③について、基板を作製してネットワークアナライザ (8753ES アジレント製) を用いて計測を行った。

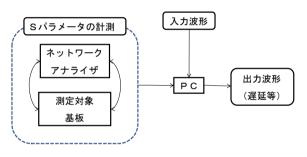

基板に実際の信号を入力して出力信号を測定した場合、入力信号の品質や接続ケーブルが基板の評価の誤差となるおそれがある。したがって、実験方法としては、ネットワークアナライザで基板のSパラメータを実測し、これに基づき計算機上で入力波形に対する出力波形を算出し、遅延時間などの評価を行った(図1)。

入力信号波形は、周波数 200MHz 立ち上がり時間 1 ns、振幅 1.8V とし、遅延時間の評価に用いる閾値 (low→high) は 1.15V とした。配線幅は 0.2mm、誘電体の厚みは 0.1mm で FR-4 を用いた。①~③の各基板のパラメータは以下のとおり。

# ① クロストーク基板

2本の平行なマイクロストリップラインの長さ L、線間の距離 D を以下の組み合わせで変化させた。(単位は mm)

(L,D) = (30,0.6), (30,0.4), (30,0.2),

(80,0.4) , (80,0.2) .

### ② ミアンダ基板

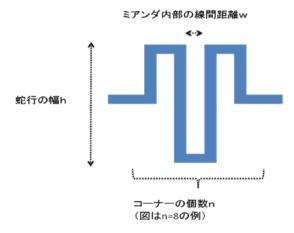

図 2 に示すとおり、コーナーの個数 n、蛇行の幅 h、内部の線間距離 w について、以下の組み合わせで変化させた。 (単位は mm)

$$(n,h,w) = (8,10,0.6)$$

,  $(8,10,0.4)$ ,  $(8,10,0.2)$ ,  $(4,20,0.6)$ ,  $(4,20,0.4)$ ,  $(4,20,0.2)$ .

## ③ ルーホール基板

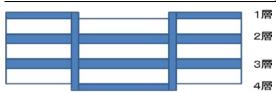

スルーホールのホール径および個数を変化させた (図 3)。ホール径が  $0.3 \,\mathrm{mm}$  のときに、個数を  $0.3 \,\mathrm{mm}$  のときに、個数を  $0.3 \,\mathrm{mm}$  の 個 数 が 4 個 の と き に ホール 径 を  $0.3 \,\mathrm{mm}$ ,  $0.2 \,\mathrm{mm}$ ,  $0.1 \,\mathrm{mm}$  に変化させた。

図1. 実験方法の概念図

図2. ミアンダのパラメータ.

図3.スルーホール基板. 4層基板を信号線に沿って切断した面。 両面に内部の2層にグランドプレーンをもつ。 スルーホールの個数2の例。 スルーホールの直径も変化させる。

# 3 結果及び考察

## 3.1 クロストーク

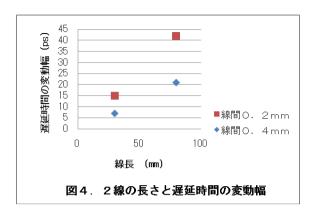

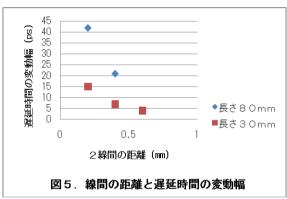

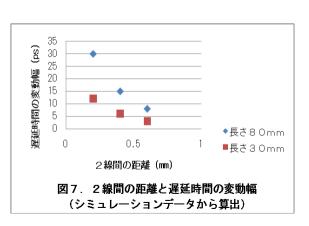

2線の線長と遅延時間の変動幅のあいだには比例の関係(図 4)、2線間の距離と遅延時間の変動幅のあいだには反比例の関係(図 5)がたしかめられた。

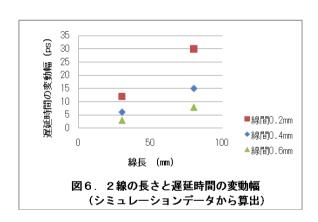

シミュレータ (sonnet lite plus, Sonnet Software inc.) を用いて同様の条件で S パラメータを求め、遅延時間の変動幅を評価したところ 同様の傾向がみられた (図 6、図 7)。

## 3.2 ミアンダ

ミアンダにおいて、幾何学的に等しい配線長の 直線と比較すると遅延時間が短縮する現象がみら れた。ミアンダの条件と、短縮した時間(遅延短 縮)を表1にまとめた。

表 1 から遅延短縮を抑えるには以下のことが条件であることがわかる。

- コーナーの個数を抑える

- ・蛇行の振幅を抑える

- ・線間距離をひろげる

さらに、表 1 の (16,10,0.2) と (8,20,0.2) を比較すると後者のほうが遅延短縮は少ない。このことから、ミアンダの規模が一定であるならば、コーナー回数を減らし、蛇行の幅を大きくとったほうが遅延短縮を抑えることができると考えられる。

ただし、蛇行の幅を大きくとると、反射量が大きい周波数帯域があらわれた (図 8, 4 GHz 付近)。蛇行の幅が半波長になるときに反射のピークがあらわれると考えられる。

今回の伝送帯域では波形にほとんど影響が見ら

れなかったが、信号の伝送帯域によっては波形そのものに影響があらわれてしまうと考えられる。

|       |      | , ,  | • /  |

|-------|------|------|------|

| コーナーの | 蛇行の幅 | 線間距離 | 遅延短縮 |

| 個数    | [mm] | [mm] | [ps] |

|       |      | 0.6  | 42   |

|       | 20   | 0.4  | 85   |

| 16    |      | 0.2  | 117  |

|       |      | 0.6  | 23   |

|       | 10   | 0.4  | 37   |

|       |      | 0.2  | 77   |

| ·     |      | 0.6  | 23   |

| 8     | 20   | 0.4  | 33   |

0.2

42

表1. ミアンダにおける遅延時間の短縮

| -5 -10 (GP) -15 -20 -35 -40 -45 | A |   | <b>A</b> |      | Y. |   | → 蛇行の幅<br>2 0 mm<br>- 蛇行の幅<br>1 0 mm |

|---------------------------------|---|---|----------|------|----|---|--------------------------------------|

|                                 | 0 | 1 | 2        | 3    | 4  | 5 | 6                                    |

|                                 |   |   | 周波数      | (GHz | )  |   |                                      |

# 3.3 スルーホール

時間からの増分を表2にまとめた。この増分につ いては、スルーホールの個数が4のときを例にと れば、基板の厚さ (1.4mm) の 4 倍の配線長 (5.6mm) が加わったためである。マイクロスト リップライン (実効誘電率 3.1 とする) に おいて、5.6mm の配線長は約33 ps に相当する。 この値と表2の値を比較すると、同じ配線長にお いては、スルーホールを含む配線の遅延時間はマ イクロストリップラインのみによる配線の遅延時 間よりも20ps程度大きく見積もる必要がある。

スルーホールの個数が0(直線)のときの遅延

ホール径による遅延時間の差は 4ps 以内であっ た。

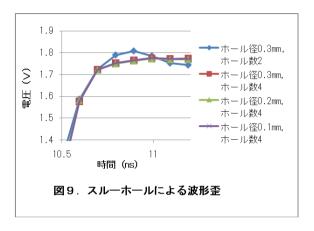

ホール数と遅延時間の関係をみると単純な比例 の関係ではない。これは波形のひずみによる影響 と考えられる(図9)。

表2. スルーホールにおける遅延時間の増分

| スルーホールの条件         | 遅延増加<br>(ps) |  |  |

|-------------------|--------------|--|--|

| ホール径 0.1mm ホール数 4 | 55           |  |  |

| ホール径 0.2mm ホール数 4 | 51           |  |  |

| ホール径 0.3mm ホール数 4 | 54           |  |  |

| ホール径 0.3mm ホール数 2 | 35           |  |  |

# 4 まとめ

クロストーク、ミアンダおよびスルーホールそ れぞれの遅延時間・波形の評価を行った。クロス トークでは遅延時間の変動幅については最大で 42ps、ミアンダでは幾何科学的に等しい配線長の 等しい直線配線と比較したときの遅延時間の短縮 は最大で117ps、4つのスルーホールによる遅延時 間の増分については約20 psであった。

単純な比較はできないが、266MHzクロックに おけるクロストークおよび配線長不整合によるタ イミングバジェットはそれぞれ、±55psおよび± 25psであることから、設計上無視できないことが わかった。

# (1) クロストーク

遅延時間の変動幅は最大で42psであり、設計上 無視できないものであることがわかった。

遅延時間の変動幅は信号の内容によって動作中 に必ず変動するものなので、減らしておかなけれ ばならない。

遅延時間の変動幅が、2線の長さに比例し、2線 間の距離に反比例する結果を得た。

# (2) ミアンダ

幾何科学的な配線長からの遅延時間の短縮につ

いては最大で117psであり、設計上無視できない ものであることがわかった。

一定の規模のミアンダにおいて線間距離が一定ならば、遅延時間の短縮による誤差を抑えるには、コーナーの回数を減らし、蛇行の幅を大きく長くすることが効果的であることがたしかめられた。 但し、蛇行の幅が半波長になると反射が大きくなり、伝送帯域によっては波形に影響を与えるので注意が必要である。

## (3) スルーホール

幾何学的な配線長により見積もられる遅延時間 よりも遅延が増加することが確かめられた。

4つのスルーホールで20ps増加することから、 設計上無視できないものであることがわかった。 ホールの配置によって信号波形にひずみが生じ るため、ホールの数と遅延時間の関係は、単純な 比例ではない。

## 謝辞

SONNETを用いたシミュレーションにあたり小暮特許事務所所長 小暮裕明氏からシミュレーションのノウハウ・データの解釈等において多大な御指導をいただきました。ここに深謝の意を表します。

# 参考文献

- JEDEC , http://www.jedec.org/standardsdocuments/technology-focus-areas/memorymodule-design-file-registrations, 2009. 10. 15

- 2) Micron Technology, Inc: Technical Note, TN-47-01, DDR2-533 Memory Design Guide for Two-DIMM Unbuffered Systems, 2005 (20)

- 3) Micron Technology, Inc: Technical Note, TN-47-01, DDR SDRAM Point-to-Point Simulation Process, 2005(8)