高速デジタル回路

高速デジタル回路とは

- 基板材料と回路幅で、反射による損失と伝送損失を最適化

- 伝搬遅延による誤動作を等長配線および等遅延配線により最適化

- 信号長・配線方法を最適化することでクロストークを最小化

- 基板材料と層構成で、高速伝送・差動伝送を最適化

基板設計2つのポイント

1) 波形の乱れを最小化する

- a)反射対策

-

反射はオーバーシュート・アンダーシュートとなって、時には電磁適合性に大きく悪影響を及ぼします。

またデジタル信号の「H」「L」の識別にも影響します。

このような事から、差動90Ω 差動100Ω シングル50Ωなどの高速信号の伝送線路はインピーダンスをマッチングさせて反射を抑えています。当社ではインピーダンスのマッチングを下記手順で行なっています。

- 回路図やお客さまとのコミュニケーションからインピーダンスマッチングの必要な信号線を特定する

- 信号に使用される周波数から基板材を確定する

- 部品を基板に配置して基板の層数および層構成を確定させる

- 層構成や基板材料の誘電率からパターン幅とGAPを求める

- 求められた数値で基板製作が可能かどうかを連携工場と協議する

- 完成した基板で特性インピーダンスの誤差が10%以下である事を確認する

このように反射が最小となるように基板を設計します。

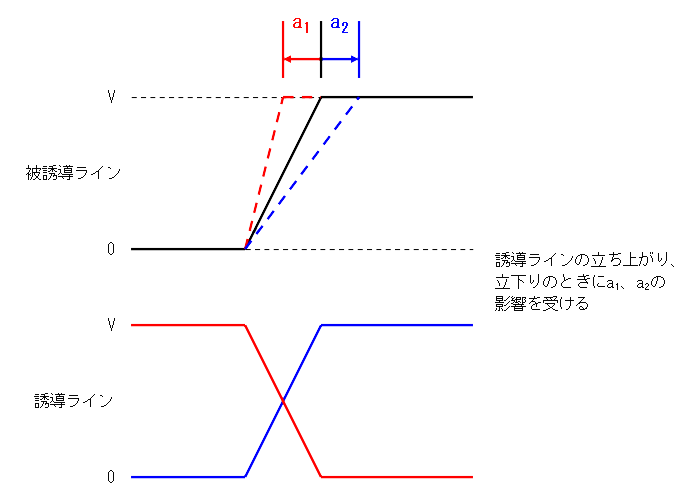

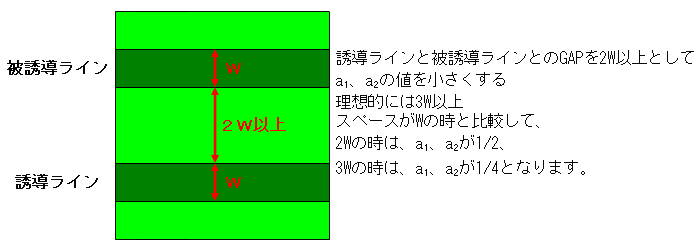

- b)クロストーク対策

-

クロストークは2線間の立ち上がり立ち下がり時に相互に大きく影響し合います。

この影響を最小限に抑えるように基板設計をします。

方法:「ライン幅をWとした時に、GAPをmin2Wとする」

理由: 埼玉県産業技術総合センターと共同研究を行いFRー4で実機を作成してクロストークによる影響を調査しました。その調査結果によって決めました。

- c)シンボル間干渉(ISI)対策

-

配線長を考慮する事で対策としています。

シンボル間干渉は、同一ライン上の信号で先に送り出された信号が次に送り出された信号に影響を受け波形を乱す現象です。

信号が高速化する中で問題視されるようになってきました。理想的には先に送り出された信号が受け取り側で完全に受け取られた後に次の信号を送り出す事ができれば良いのですがそうはいきません。

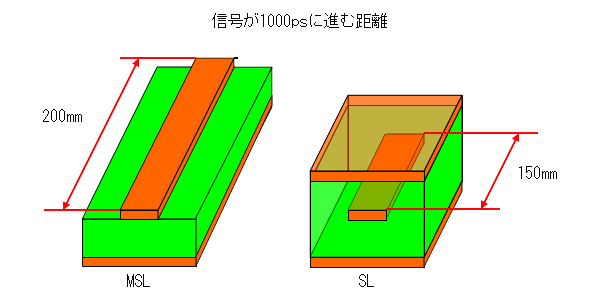

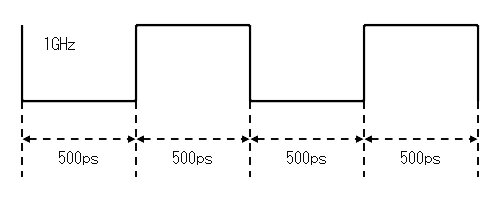

1GHzのデジタル信号を想定して考えてみましょう。- 基本周波数を1GHzとする

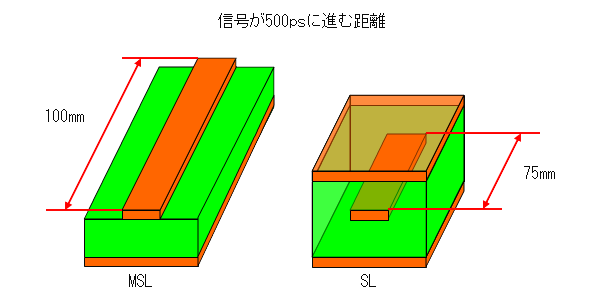

- 周期は1nsで「H」「L」がそれぞれが500psとなり

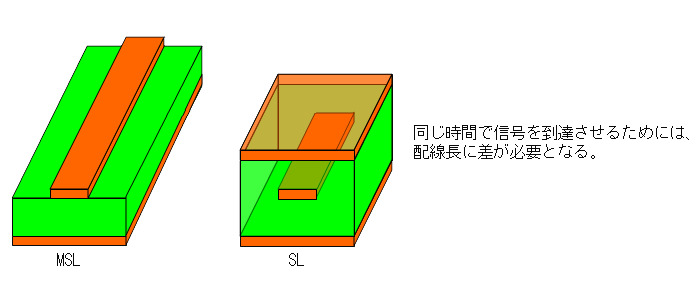

- V=K・C/√εから考えるとマイクロストリップライン(MSL)上の電気信号の進む距離は1nsで約200mm、ストリップライン上では約150mmとなります。

「H」の信号が2回続けて出力されるとします。

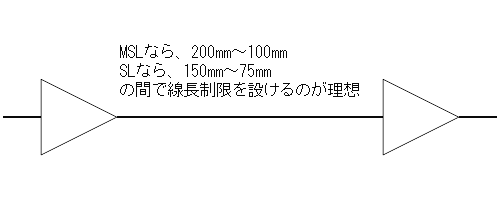

1回目の立ち上がりから2回目の立ち上がりまでを線長制限とするならばMSLでは200mm、SLでは150mmとなります。1回目のたち下がりから2回目の立ち上がりまでを線長制限とするならば、MSLでは100mm、SLでは75mmとなります。

周波数が高くなれば線長制限も短くなり理想の線長を確保できないケースが多くなります。しかし、上の例のように線長制限を意識する事でシンボル間干渉を最小化できる事を念頭に基板を設計する事が重要です。

2)「等長・等遅延配線で遅延量を合わせること」

先ず最初に「等長配線=等遅延配線」ではありません。

よって、等遅延配線を行うために次の3つを考慮して基板設計を行っています。

- 遅延時間を合わせる必要のあるラインは同層で配線

-

理由:MSLとSLでは実効誘電率の違いから信号の進む速度がかわるため

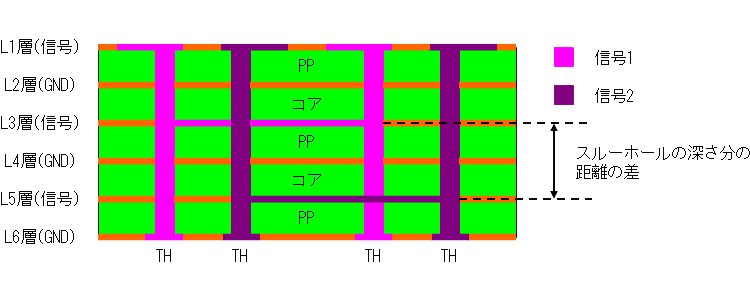

- 高多層の場合はスルーホールに注意

-

理由:スルーホールの深さの差が等遅延に影響する場合があるから

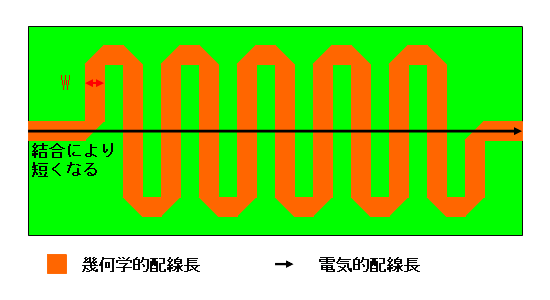

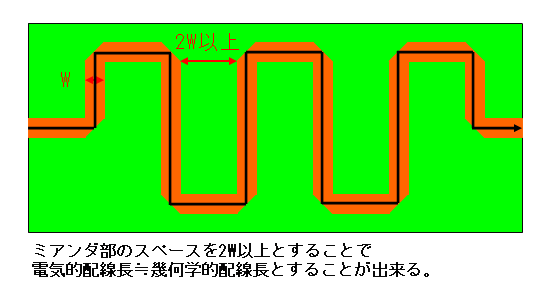

- ミアンダ部のスペースをライン幅の原則3倍以上とする

-

理由:ミアンダ部のスペースが狭いと、電気的結合により、幾何学的に同じ配線長の信号よりも、早く信号が到達するため等遅延にならないから

上のようなことを気をつけることにより等長配線=等遅延配線とする事ができて基板設計者も等長のミスがなくなり回路設計者もチェックが容易になります。

実際に上で説明したことを考慮して基板設計を行なっています。

これまでの説明で、等長配線=等遅延配線とする事ができましたので、以下等長 配線と称します。

等長配線とは、どれだけの精度で等長にしなければならないのでしょうか。

当社では信号に使用されている基本周波数によって決定しています。

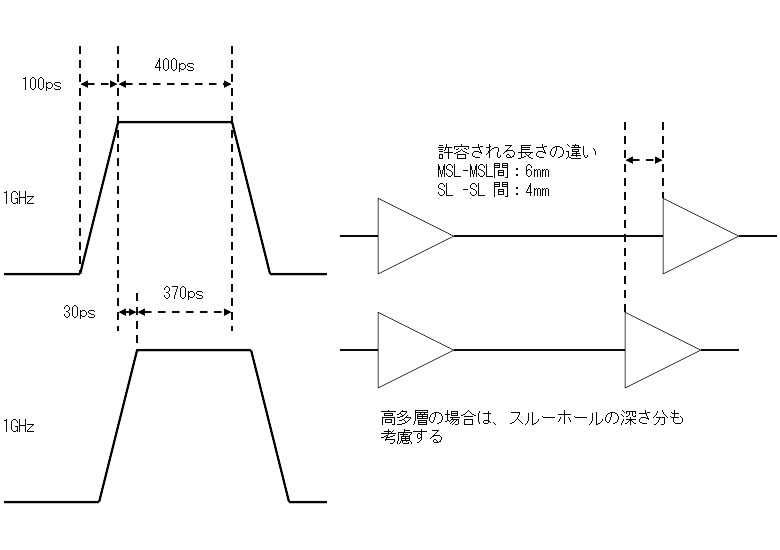

例えば基本周波数1GHzのデジタル信号を考えてみます。1周期=1nsですから、「H」の時間は500psです。仮に立ち上がりを20%、たち下がりを20%とすると信号の「H」の時間は60%の300psと考える事ができます。立ち上がりの20%は100psとなります。

ここで100psの約1/3の30psの遅延が発生したとします。それでも等長を必要とする他のラインの「H」部との重なりは270ps確保出来ているので、信号のHとLの判定には問題ないでしょう。

このように考えた時に、30psに信号が進む距離は、MSLでは6.0mm、SLでは4.0mmとなります。2GHzならばこの半分、4GHzならまたその半分と考えます。

さらに、スルーホールの深さ分を加味して等長の精度を決定するのが現実的と思います。

実績紹介

- DDR3

- DDR4

- USB3.0を使用した基板

- PCIe_gen3を使用した基板

- DDR4_2400を32個搭載した基板

- DDR3_1600を16個搭載した基板

- DDR2_800を搭載したモバイルアクセサリの基板

- DDR2_800を搭載した高速応答タイプ電源の基板

- FPGA・PLD・DSPを使用した高速信号処理の基板

- 大規模BGA・FPGA・PLD・DSPを使用した高速信号処理の基板

プライバシーポリシー

プライバシーポリシー お問い合わせ

お問い合わせ